您所在的位置:首页 - 热点 - 正文热点

cpld编程语言

![]() 志琦

04-26

【热点】

787人已围观

志琦

04-26

【热点】

787人已围观

摘要当涉及到CPLD(可编程逻辑器件)编程时,有很多不同的实例和应用。CPLD是一种硬件设备,它可以通过编程来实现特定的逻辑功能。下面是一个简单的CPLD编程实例:**实例:实现一个简单的计数器****目

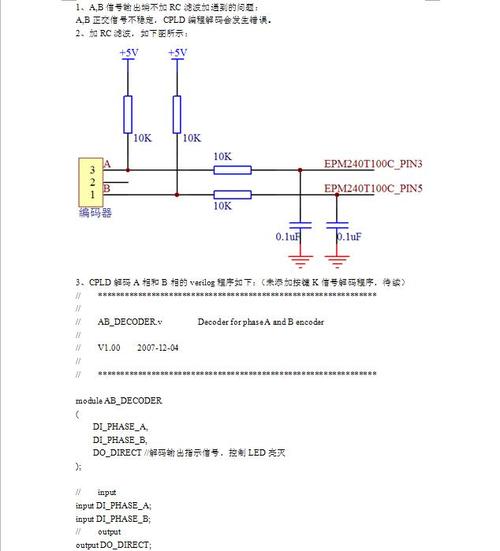

当涉及到CPLD(可编程逻辑器件)编程时,有很多不同的实例和应用。CPLD是一种硬件设备,它可以通过编程来实现特定的逻辑功能。下面是一个简单的CPLD编程实例:

实例:实现一个简单的计数器

目标:

使用CPLD编程实现一个简单的计数器,它能够在每个时钟周期中递增一个计数值,并且能够在达到最大值时重新开始计数。步骤:

1.

定义计数器的位宽:

确定计数器的位宽。假设我们选择一个8位的计数器,这意味着它能够从0计数到255。2.

设计计数逻辑:

设计逻辑来实现计数器的功能。在每个时钟周期,计数器的当前值将递增。当计数器达到最大值时,它将重新从零开始计数。3.

编写Verilog/VHDL代码:

使用Verilog或VHDL编写计数器的代码。这些代码将描述计数器的逻辑行为。4.

综合和布局:

使用CPLD开发工具对编写的代码进行综合和布局。这个过程将把代码转换成逻辑门级别的电路,并将其映射到CPLD的可用资源上。5.

下载到CPLD:

将综合后的设计下载到CPLD芯片中。这通常通过JTAG或类似的编程接口完成。6.

验证功能:

验证CPLD中的计数器功能。这可以通过连接一个示波器或逻辑分析仪来观察计数器的行为,或者在连接到计数器输出的显示器上观察计数值的变化来完成。7.

调试和优化:

如果计数器的功能不如预期,可以进行调试和优化。这可能涉及修改Verilog/VHDL代码,重新综合和布局,或者调整设计的时钟频率等。示例Verilog代码(简化版本):

```verilog

module simple_counter (

input wire clk,

input wire rst,

output reg [7:0] count

);

always @(posedge clk or posedge rst)

begin

if (rst)

count <= 8'b00000000; // Reset counter to zero

else if (count == 8'b11111111) // If count reaches maximum value

count <= 8'b00000000; // Reset counter to zero

else

count <= count 1; // Increment counter

end

endmodule

```

这是一个简单的8位计数器的Verilog代码。它具有一个时钟输入(clk)和一个复位输入(rst),并且输出一个8位的计数值(count)。在每个时钟上升沿,计数器的值会递增。当计数器达到最大值时,它会被重置为零。

Tags: 剑圣打野天赋 生化危机8剧情 数码宝贝月光金手指 博茨瓦纳地图

版权声明: 免责声明:本网站部分内容由用户自行上传,若侵犯了您的权益,请联系我们处理,谢谢!联系QQ:2760375052

上一篇: c专家编程

下一篇: ug怎么在圆柱面上画图

最近发表

- 三星手机的用户群像,谁在用,为什么选择它?

- 上海通用雪佛兰景程——家用轿车的理想选择

- 雪佛兰新赛欧油耗深度解析,经济实惠的出行选择

- 一款值得信赖的全能座驾

- Jeep牧马人,越野传奇的全面解析

- 轻松掌握 XP 中文语言包下载与安装全攻略

- 深入探索Google操作系统,如何改变我们的数字生活

- 一款独特的美式SUV

- 轻松入门电脑知识,畅游数字世界——电脑知识学习网带你全面掌握

- 深入解读vivo Y93手机参数,性能、功能与用户体验

- 电源已接通但未充电?别慌!详解及解决方法

- 苹果SE4上市时间及价格全解析,性价比之王的回归

- 探寻AM3平台的最佳CPU选择

- 别克君威价格全解析,购车必备指南

- 全面解析与深度评测

- 理解负指数分布图像,隐藏在日常生活中的数学之美

- 全面解析与购车指南

- 深入了解标志206最新报价,购车指南与市场分析

- 深入了解 i3 10100,一款适合日常生活的高效处理器

- 走进vivo手机商城,探索智能生活的新篇章

- 5万以下汽车报价大全,为您精选高性价比的经济型车型

- 一辆小车的精彩故事

- 全面解析与购车建议

- 深入了解昊锐1.8T油耗表现及其优化技巧

- 迈腾18T,都市出行的理想伙伴,轻松驾驭每一段旅程

- 桑塔纳新款,传承经典,焕发新生

- 联发科MT6765,智能手机的高效心脏

- 丰田Previa,一款经典MPV的前世今生

- 小学校长受贿近千万,背后的故事与启示

- 探索移动帝国论坛,连接全球移动技术爱好者的桥梁

- 小小的我预售破4000万,一场梦幻童话的奇迹之旅

- 深度解析凯迪拉克CTS(进口),豪华与性能的完美结合

- 揭秘南方人为何更易患鼻咽癌?

- 豪华与性能的完美结合——价格详解及购车指南

- 我是刑警编剧专访,坚持创作初心,不惯市场之风

- 轻松掌握图标文件的奥秘

- 黄圣依在最强大脑中的高知魅力——路透背后的故事

- 微信紧急提醒,警惕木马病毒——如何防范与应对网络攻击?

- Jeep新大切诺基,经典与现代的完美融合

- 顾客用餐时打火机不慎落入锅内引发爆炸事件解析

- 解读大捷龙报价,购车前必知的关键信息

- 大学生作业中的AI气息,新时代的学习变革

- 比亚迪思锐,探索未来汽车科技的先锋

- 警惕串联他人越级走访,数人多次煽动行为终被抓获的警示

- 经典与现代的完美融合——联想ThinkPad X201,一款改变工作方式的笔记本电脑

- 北京平谷再现鸟中老虎

- 一位七旬官员的人生转折,公诉背后的故事与深思

- 财神鱼离奇死亡,男子悲痛之余做出惊人决定,起锅烧油含泪吃下

- 掌握 Flash 课件制作,从零开始的实用教程

- 蜜雪冰城的新动作,背后的战略调整与市场应对